## LINEAR INTEGRATED CIRCUIT HANDBOOK

# LINEAR INTEGRATED CIRCUIT HANDBOOK

Designed and produced by Peter Wigens Consultants

© The Plessey Company plc

March 1983

Publication No. P.S. 1973

This publication is issued to provide outline information only and (unless specifically agreed to the contrary by the Company in writing) is not to form part of any order or contract or be regarded as a representation relating to the products or services concerned. We reserve the right to alter without notice the specification, design, price or conditions of supply of any product or service.

The name Plessey and the Plessey logo are registered trademarks of The Plessey Company plc.

## **Contents**

| Page |

|------|

| 5    |

| 8    |

| 10   |

| 11   |

| 13   |

| 14   |

| 17   |

| 193  |

| 203  |

|      |

## Product index

| OPERATIONAL A                                                                      | MPLIFIERS                                                                                                                                                                                                                              | Page                                    |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| SL541B<br>TAB1042<br>TAB1043                                                       | High slew rate operational amplifier Quad programmable operational amplifier Quad programmable operational amplifier                                                                                                                   | 81<br>185<br>189                        |

| LINEAR RF AMPL                                                                     | IFIERS                                                                                                                                                                                                                                 | 0.4                                     |

| SL541B<br>SL550D & G<br>SL560C<br>SL561B,C                                         | High slew rate operational amplifier<br>Low noise wideband amplifier with external gain control<br>300MHz low noise amplifier<br>Ultra low noise preamplifiers                                                                         | 81<br>85<br>91<br>95                    |

| PHASE LOCKED                                                                       | LOOP CIRCUITS                                                                                                                                                                                                                          |                                         |

| SL650B,C<br>SL651B,C<br>SL652C                                                     | Modulator/phase locked loop circuits for modems<br>Modulator/phase locked loop circuits for modems<br>Modulator/phase locked loop                                                                                                      | 115<br>115<br>119                       |

| LIMITING WIDEB                                                                     | AND AMPLIFIERS                                                                                                                                                                                                                         |                                         |

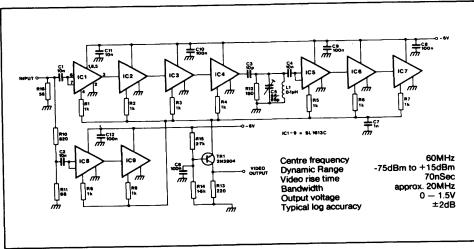

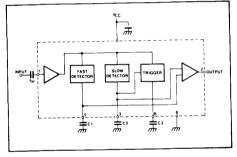

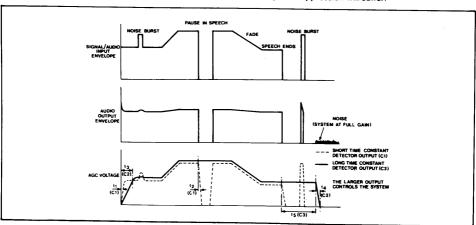

| SL521A,B & C<br>SL523B,C & HB<br>SL525C<br>SL531C<br>SL532C<br>SL565C<br>SL1521A,C | 140MHz wideband log amplifier 120MHz dual wideband log amplifier Wideband log IF strip amplifier 250MHz true log IF amplifier Low phase shift limiter 1GHz wideband amplifier 300MHz wideband amplifier 300MHz dual wideband amplifier | 63<br>67<br>71<br>75<br>79<br>99<br>129 |

| SL1523C                                                                            | SUDIVITIZ dual Widebaria ampinior                                                                                                                                                                                                      |                                         |

| <b>MATCHED TR</b> | ANSISTOR AND ARRAYS                            |            |

|-------------------|------------------------------------------------|------------|

| SL301K,L          | Dual NPN transistors                           | 19         |

| SL360C,G          | High performance NPN dual transistor arrays    | 27         |

| SL362C            | High performance NPN dual transistor arrays    | 27         |

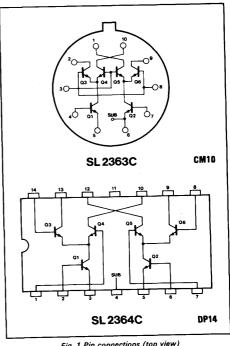

| SL2363C           | Very high performance transistor array         | 145        |

| SL2364C           | Very high performance transistor array         | 145        |

| SL3045C           | General purpose NPN transistor array           | 147        |

| SL3046C           | General purpose NPN transistor array           | 147        |

| SL3127C           | High frequency NPN transistor array            | 149        |

| SL3145C,E         | 1.2GHz high frequency NPN transistor arrays    | 153        |

| RADIO-COMM        | UNICATIONS                                     |            |

| SL610C            | RF amplifier                                   | 103        |

| SL611C            | RF amplifier                                   | 103        |

| SL612C            | IF amplifier                                   | 103        |

| SL621C            | AGC generator                                  | 107        |

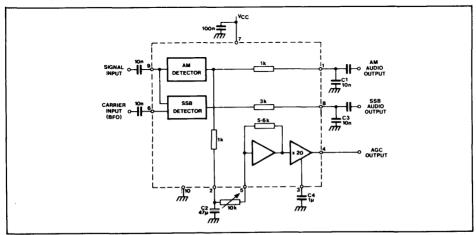

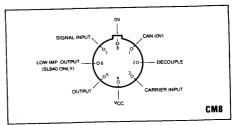

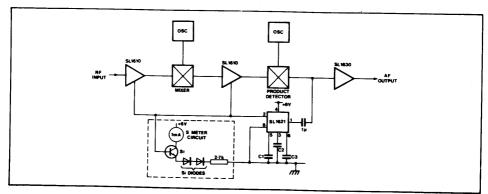

| SL623C            | AM detector/AGC amplifier/SSB demodulator      | 111        |

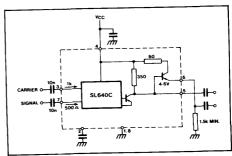

| SL640C            | Double balanced modulators                     | 113        |

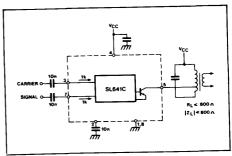

| SL641C            | Double balanced modulators                     | 113        |

| SL1613C           | Wideband log IF strip amplifier                | 137        |

| SL1621C           | AGC generator                                  | 141        |

| SL6270C           | Gain controlled preamplifier                   | 157        |

| SL6310C           | Switchable audio amplifier                     | 161        |

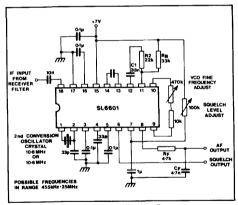

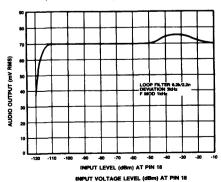

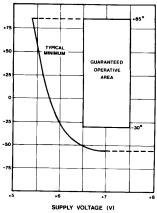

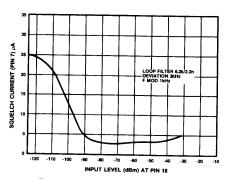

| SL6601C           | Low power IF/AF PLL circuit for narrow band FM | 169        |

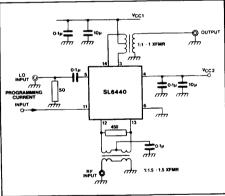

| SL6440A,C         | High level mixer                               | 165        |

| SL6691C           | Monolithic circuit for paging receivers        | 173        |

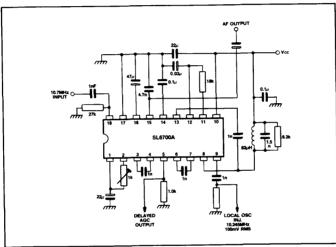

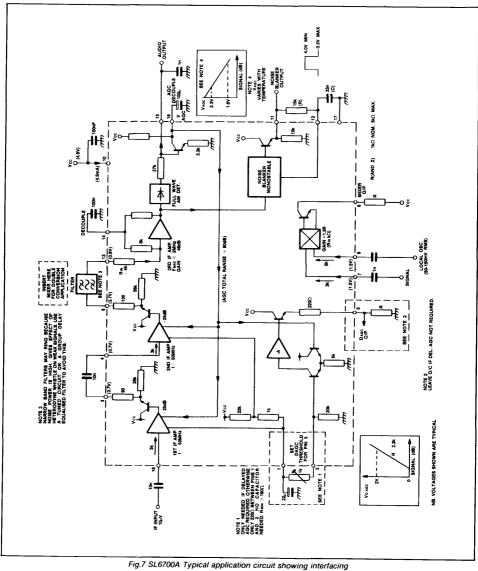

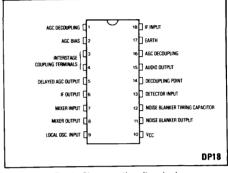

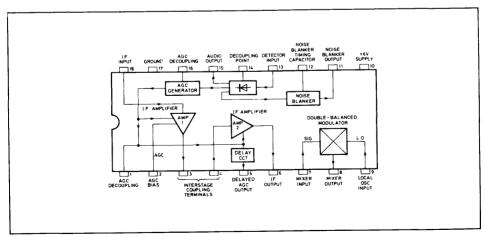

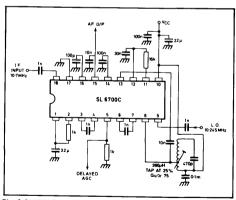

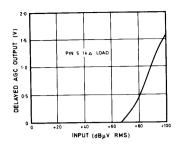

| SL6700A           | IF amplifier and AM detector                   |            |

| SL6700C           | IF amplifier and AM detector                   | 177<br>181 |

|                   |                                                | 101        |

### **POWER CONTROL CIRCUITS**

| SL440  | Power control circuit | 29 |

|--------|-----------------------|----|

| SL441A | Zero voltage switch   | 33 |

|        | Zero voltage switch   | 37 |

| SL441C | Zero voltage switch   | 41 |

| SL443A |                       | 45 |

| SL445A | Zero voltage switch   | 55 |

| SL446A | Zero voltage switch   | 00 |

## Product list

| 01.00414      |                                                         | Page |

|---------------|---------------------------------------------------------|------|

| SL301K        | Dual NPN transistors                                    | 19   |

| SL301L        | Dual NPN transistors                                    | . 19 |

| SL303L        | 400MHz tripple NPN transistors                          | 23   |

| SL360C,G      | High performance NPN dual transistor arrays             | 27   |

| SL362C        | High performance NPN dual transistor arrays             | 27   |

| SL440         | Power control circuit                                   | 29   |

| SL441A        | Zero voltage switch                                     | 33   |

| SL441C        | Zero voltage switch                                     | 37   |

| SL443A        | Zero voltage switch                                     | 41   |

| SL445A        | Zero voltage switch                                     | 45   |

| SL446A        | Zero voltage switch                                     | 55   |

| SL521A,B & C  | 140MHz wideband log amplifier                           | 63   |

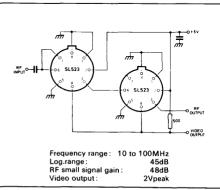

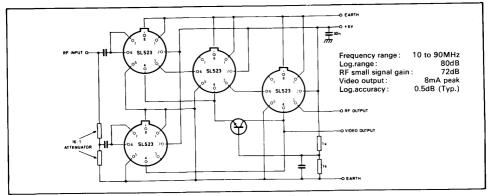

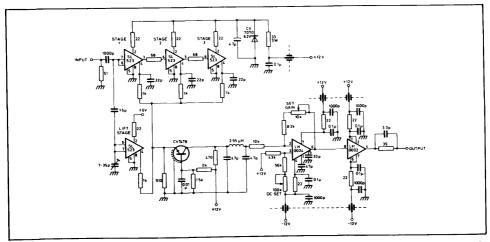

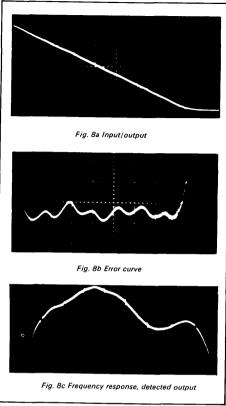

| SL523B,C & HB | 120MHz dual wideband log amplifier                      | 67   |

| SL525C        | Wideband log IF strip amplifier                         | 71   |

| SL531C        | 250MHz true log IF amplifier                            | 75   |

| SL532C        | Low phase shift limiter                                 | 79   |

| SL541B        | High slew rate operational amplifier                    | 81   |

| SL550D & G    | Low noise wideband amplifier with external gain control | 85   |

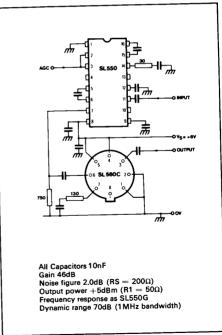

| SL560C        | 300MHz low noise amplifier                              | 91   |

| SL561B,C      | Ultra low noise preamplifiers                           | 95   |

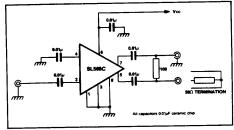

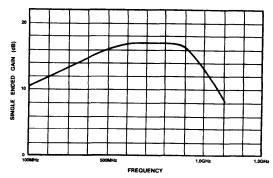

| SL565C        | 1GHz wideband amplifier                                 | 99   |

| SL610C        | RF amplifier                                            | 103  |

| SL611C        | RF amplifier                                            | 103  |

| SL612C        | IF amplifier                                            | 103  |

| SL621C        | AGC generator                                           | 107  |

| SL623C        | AM detector/AGC amplifier/SSB demodulator               | 111  |

| SL640C        | Double balanced modulators                              | 113  |

| SL641C        | Double balanced modulators                              | 113  |

| SL650B,C      | Modulator/phase locked loop circuits for modems         | 115  |

| SL651B,C      | Modulator/phase locked loop circuits for modems         | 115  |

| SL652C        | Modulator/phase locked loop                             | 119  |

| SL1521A,C     | 300MHz wideband amplifier                               | 129  |

| SL1523C       | 300MHz dual wideband amplifier                          | 133  |

| SL1613C       | Wideband log IF strip amplifier                         | 137  |

| SL1621C       | AGC generator                                           | 1/1  |

| SL2363C   | Very high performance transistor array         | 145 |

|-----------|------------------------------------------------|-----|

| SL2364C   | Very high performance transistor array         | 145 |

| SL3045C   | General purpose NPN transistor array           | 147 |

| SL3046C   | General purpose NPN transistor array           | 147 |

| SL3127C   | High frequency NPN transistor array            | 149 |

| SL3145C.E | 1.2GHz high frequency NPN transistor arrays    | 153 |

| SL6270C   | Gain controlled preamplifier                   | 157 |

| SL6310C   | Switchable audio amplifier                     | 161 |

| SL6440A,C | High level mixer                               | 165 |

| SL6601C   | Low power IF/AF PLL circuit for narrow band FM | 169 |

| SL6691C   | Monolithic circuit for paging receivers        | 173 |

| SL6700A   | IF amplifier and AM detector                   | 177 |

| SL6700C   | IF amplifier and AM detector                   | 181 |

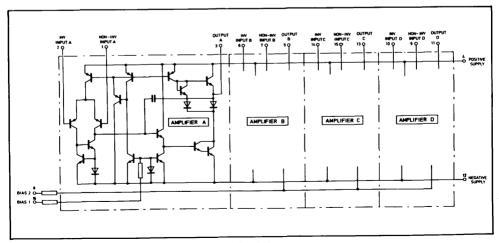

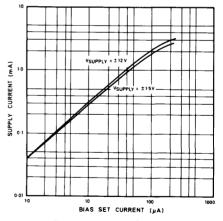

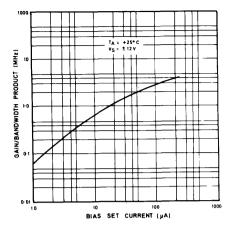

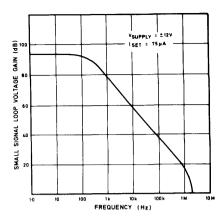

| TAB1042   | Quad programmable operational amplifier        | 185 |

| TAB1042   | Quad programmable operational amplifier        | 189 |

| 1 AD 1043 | Quad programmable operational amplimen         |     |

### Quality data

Plessey Semiconductors has Factory Approval to:-

**BS9300** for semiconductor devices of Assessed Quality (BSI Certificate 1053/M)

BS9400 for integrated circuits of Assessed Quality (BSI Certificate 1053/M)

**CECC 50000** Inspection Organisation to document level 1 (BS9300) M0020/CECC refers

**DEF STAN 05** — **21 QC** System requirements for Industry (Equivalent to AQAP — 1) Certificate 65752/1/01 refers

Devices are also manufactured and tested in accordance with the methods of **MIL-STD-833**, the US Military Standard; Test Methods and Procedures for Microcircuits, and **MIL-M-38510**, US Military Specification, Micro-electronics; General Specifications for.

## Ordering information

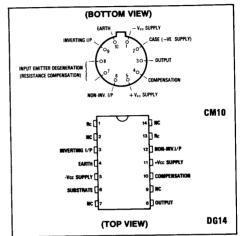

All Plessey Semiconductors integrated circuits are allocated type numbers which must be quoted when ordering. This number may or may not have a suffix (A, B, C, etc.) which denotes the precise electrical specification or temperature grade. When there is a choice of packages the two-digit Pro-Electron code is used to identify the style required, according to the following table:

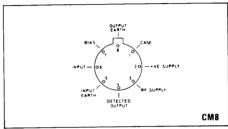

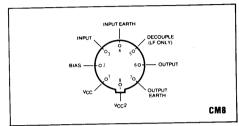

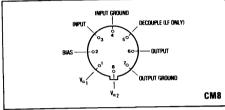

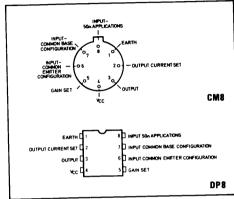

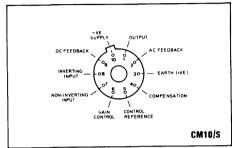

CM - Multilead TO-5

DC - Ceramic Dual-in-Line (metal lid)

DG - Ceramic Dual-in-Line

GC - Ceramic Chip Cover

Within the UK, orders for quantities up to 99 will be referred to your local Distributor. Quantities of 1000 and over must be ordered from:

Plessey Semiconductors Limited Cheney Manor Swindon, Wiltshire SN2 2QW United Kingdom Telephone: Swindon (0793) 36251 Telex: 449637

A reciprocal arrangement exists with all Distributors, but it will expedite delivery of order if buyers can direct orders as indicated above. Outside the UK, irrespective of quantity, you are invited to contact your nearest Plessey Semiconductors Sales Outlet (see pages 203-207).

### **DELIVERED PRODUCT QUALITY**

It is our policy to deliver a reliable quality product and to achieve this end all devices undergo 100% electrical testing of every relevant AC and DC parameter prior to shipment. The devices are tested under conditions of level and frequency closely simulating those of the typical application. Fully automatic Teradyne integrated circuit test machines, acknowledged to be among the best computer controlled test machines available, are employed.

Each and every stage of processing, assembly and testing is carefully audited by Plessey Semiconductors' independent Quality Assurance department.

Therefore we are able to guarantee the following Acceptable Quality Level (A.Q.L.) on all deliveries.

### **MECHANICAL**

Defects of a mechanical nature including coding not being legible, deformed leads, dimensional tolerances being exceeded, wrong identification of pin 1 and pins not being solderable.

0.65 % AQL,I.L.II

### ELECTRICAL

Defects of an electrical nature including device parameters being outside the acceptance specification limits, or those only stated as typical being grossly in error.

0.4 % AQL,I.L.II

The average delivered product quality is considerably better than this, the population of imperfect devices being much smaller than that indicated by the AQL values.

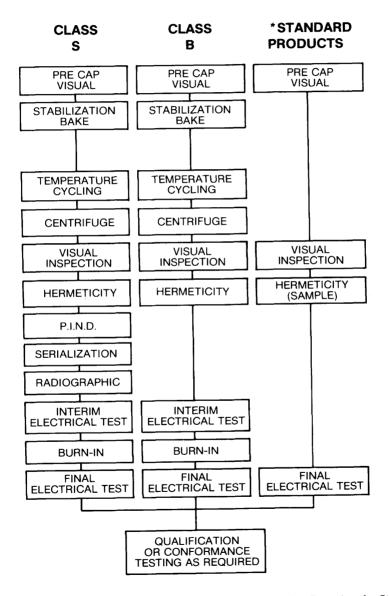

## Screening to MIL-STD-883

The following Screening Procedures are available from Plessey Semiconductors

<sup>\*</sup>Plessey Semiconductors reserve the right to change the Screening Procedure for Standard Products.

## Semi-custom design

The table outlines the essential parameters of our Semi-custom design techniques, including typical timescales for the design and production of a Semi-custom IC.

| NAME                                            | PART<br>NUMBER | TECHNOLOGY          | LOGIC<br>ELEMENTS         | TYP.GATE<br>DELAY/POWER | SYSTEM<br>CLOCK<br>SPEED |

|-------------------------------------------------|----------------|---------------------|---------------------------|-------------------------|--------------------------|

|                                                 | MJ 1XXX        | NMOS<br>(Std)       | Up to 3000 equiv.gates    | 50ns at<br>250µW        | 2MHz                     |

| Microcell                                       | MJ 1XXX        | NMOS<br>(low power) | Up to 3000<br>equiv.gates | 200ns at<br>40µW        | 2MHz                     |

|                                                 | MV 1XXX        | CMOS                | Up to 2000<br>equiv.gates | 20ns at<br>12μW/MHz     | 8MHz                     |

|                                                 | CLA 10XX       | CMOS                | 560                       | 6ns at<br>6µW/MHz       | 8MHz                     |

| Microgate-C<br>1000 Series<br>(CMOS Gate Array) | CLA 12XX       | CMOS                | 960                       | 6ns at<br>6µW/MHz       | 8MHz                     |

| ,                                               | CLÁ 15XX       | CMOS                | 1440                      | 6ns at<br>6µW/MHz       | 8MHz                     |

|                                                 | CLA 21XX       | CMOS                | 840                       | 4ns at<br>3µW/MHz       | 14MHz                    |

| Microgate-C<br>2000 Series<br>(CMOS Gate Array) | CLA 23XX       | CMOS                | 1440                      | 4ns at<br>3µW/MHz       | 14MHz                    |

| (                                               | CLA 25XX       | CMOS                | 2400                      | 4ns at<br>3µW/MHz       | 14MHz                    |

|                                                 | SCD 1XXX       | ECL                 | 75                        | 550ps/900mW             | 300MHz                   |

|                                                 | SCD 2XXXH      | ECL                 | 300                       | 550ps/3.5W              | 300MHz                   |

| Microgate-E<br>(ECL Gate Array)                 | SCD 2XXXM      | ECL                 | 300                       | .1.5ns/1W               | 250MHz                   |

|                                                 | SCD 2XXXL      | ECL                 | 300                       | 2ns/750mW               | 100MHz                   |

|                  | PART     |            | COMPONENT COUNT |             |     |  |

|------------------|----------|------------|-----------------|-------------|-----|--|

| NAME             | NUMBER   | TECHNOLOGY |                 | TRANSISTORS |     |  |

|                  | NOMBER   |            | RESISTANCE      | NPN         | PNP |  |

| Microlin         | BAA 1XXX | Bipolar    | 1219kΩ          | 81          | 28  |  |

| (Analogue Array) | BAA 2XXX | Bipolar    | 2757kΩ          | 163         | 58  |  |

<sup>\*</sup>Design and test times given are typical. Actual times will depend on the complexity of the particular circuit.

| INPUT/<br>OUTPUT<br>ELEMENTS | COMPATI-<br>BILITY | MAX.<br>PIN<br>COUNT | No. OF<br>CUSTOM<br>MASKS | TYPICAL TIME<br>FOR 1st SAMPLES |

|------------------------------|--------------------|----------------------|---------------------------|---------------------------------|

| As required                  | TTL/CMOS           | 64                   | 6                         |                                 |

| As required                  | TTL/CMOS           | 64                   | 6                         | 19 weeks*                       |

| As required                  | TTL/CMOS           | 64                   | 9                         |                                 |

| 38 I or O                    | TTL/CMOS           | 40                   | 1                         | ,                               |

| 50 I or O                    | TTL/CMOS           | 64                   | 1                         | 16 weeks*                       |

| 60 I or O                    | TTL/CMOS           | 64                   | 1                         |                                 |

| 40 I or O                    | TTL/CMOS           | 44                   | 3                         |                                 |

| 52 I or O                    | TTL/CMOS           | 56                   | 3                         | 13 weeks*                       |

| 60 I or O                    | TTL/CMOS           | 64                   | 3                         |                                 |

| 25 I or O                    | ECL 10K            | 28                   | 3                         |                                 |

| 36 I<br>20 I or O            | ECL 10K            | 64                   | 3                         |                                 |

| 36 I<br>20 I or O            | ECL 10K            | 64                   | 3                         | 16 weeks*                       |

| 36 I<br>20 I or O            | ECL 10K            | 64                   | 3                         |                                 |

| ft<br>(1mA 5V Vcc)<br>STANDARD NPN | LVczo/<br>BVczo | MAX.<br>PIN<br>COUNT | No. OF<br>CUSTOM<br>MASKS | TYPICAL TIME<br>FOR 1st SAMPLES |

|------------------------------------|-----------------|----------------------|---------------------------|---------------------------------|

| 470MHz                             | 20V/30V         | 24                   | 1                         | 15 weeks*                       |

| 470MHz                             | 20V/30V         | 24                   | - 1                       |                                 |

## Technical Data

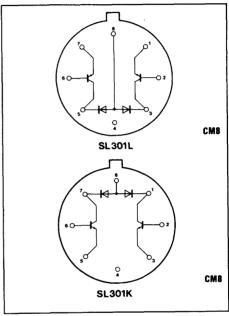

### SL301K, SL301L

### **400MHz DUAL NPN TRANSISTOR**

The SL301K and SL301L are dual monolithic NPN transistors with close parameter matching and high fr. The SL301K and SL301L have identical electrical specification.

### **FEATURES**

- Close VRF Matching<3mV</p>

- Close hfe Matching>0.9

- Good Frequency Response>400MHz

- Good Thermal Tracking

- Wide Operating Current Range

### **APPLICATIONS**

- Differential Amplifier to Very High Frequencies

- Comparators

- Current Sources

- Instrumentation

### **ABSOLUTE MAXIMUM RATINGS**

All electrical ratings apply to individual transistors. Thermal ratings apply to the total package.

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded

The isolation pin (substrate) must be connected to the most negative point of the circuit to maintain electrical isolation between transistors.

Storage temperature -55°C to +175°C (CM8)

Maximum junction temperature +175°C

Thermal resistance: see Note 1 Chip-to-case 265° C/W (CM8)

Chip-to-ambient 425° C/W (CM8)

VcB = 20V VEB = 4.0V VcER = 20V (see Fig.7)

VcE = 12V VcI = 25V Ic = 20mA

These figures are worst case, assuming all the power is dissipated in one transistor. If the power is equally shared between the two transistors, both thermal resistance figures can be reduced by 50° C/watt.

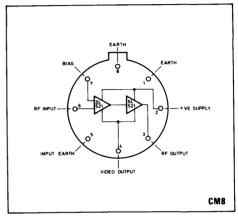

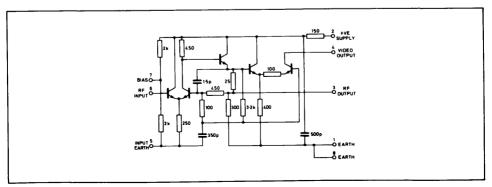

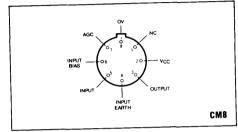

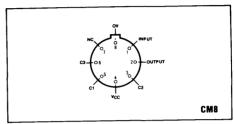

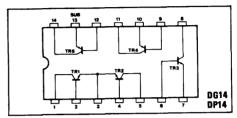

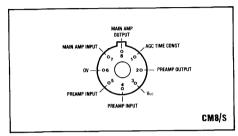

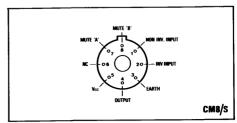

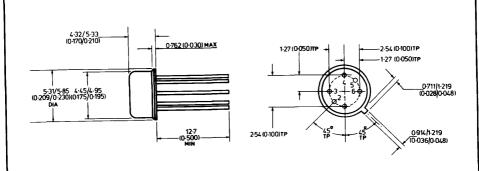

Fig.1 Pin connections

### SL301K/SL301L

### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated): Tamb = 22°C ± 2°C

| Chamata datia                       | 0 b l    | Value |      |      |       |                                   |

|-------------------------------------|----------|-------|------|------|-------|-----------------------------------|

| Characteristic                      | Symbol   | Min.  | Тур. | Max. | Units | Conditions                        |

| Collector base breakdown            | ВУсво    | 20    |      |      | V     | Ic = 10μA                         |

| Collector emitter breakdown         | BVCEO    | 12    |      |      | v     | $Ic = 10\mu A$                    |

| Collector emitter breakdown         | LVCEO    | 12    |      |      | l v   | Ic = 5mA                          |

| Emitter base leakage current        | IEBO     |       |      | 1    | μA    | VEB = 4V                          |

| Emitter base leakage current        | lebo     |       |      | 10   | nΑ    | VEB = 2V                          |

| Collector isolation breakdown       | BVcio    | 25    |      | 1    | l v   | Ic = 10μA                         |

| Forward current transfer ratio      | HFE      | 40    | 70   |      | [     | $V_{CE} = 5V$ , $I_C = 100\mu A$  |

|                                     |          | 60    | 100  |      | ·     | VcE = 5V, Ic = 1mA                |

|                                     |          | 50    | 80   |      |       | VcE = 5V, Ic = 10mA               |

| Saturation voltage                  | VCE(SAT) |       | 0.36 | 0.6  | V V   | Ic = 10mA, IB = 1mA               |

|                                     | VBE(SAT) | 0.7   | 0.8  | 0.9  | l v   | Ic = 10mA, IB = 1mA               |

| Collector base leakage current      | Ісво     |       |      | 10   | nA    | V <sub>CB</sub> = 10V             |

| Collector isolation leakage current | Icio     |       |      | 10   | nA    | Vci = 10V                         |

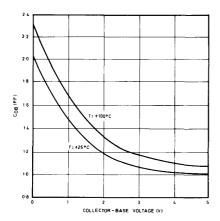

| Collector capacitance               | Сов      |       |      | 2    | pF    | $V_{CB} = 5V$                     |

| Base capacitance                    | Сів      |       |      | 4    | pF    | VBE = 0V                          |

| Collector isolation capacitance     | Ca       |       |      | 6    | pF    | $V_{CI} = +5V$                    |

| Transition frequency                | f⊤       | 400   | 680  |      | MHz   | VcE = 5V, Ic = 5mA, Freq = 100MHz |

| Matching                            |          |       |      |      | l     |                                   |

| HFE1/HFE2                           |          | 0.9   |      | 1.1  | l .   | $V_{CE} = 5V, I_{C} = 100 \mu A$  |

| '                                   |          | 0.9   |      | 1.1  |       | VcE = 5V, Ic = 1mA                |

| VBE1 - VBE2                         | ΔVBE     |       | 0.45 | 3    | mV    | $V_{CE} = 5V, I_{C} = 100 \mu A$  |

| ·                                   |          |       | 0.45 | 3    |       | VcE = 5V, Ic = 1mA                |

| Temperature coefficient of ΔVeε     |          |       | 2    | 10   | μV/°C | VCE = 5V, IC = 100µA              |

| <u> </u>                            | <u> </u> |       |      | L    |       |                                   |

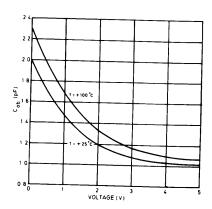

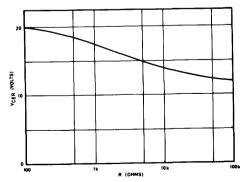

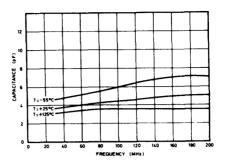

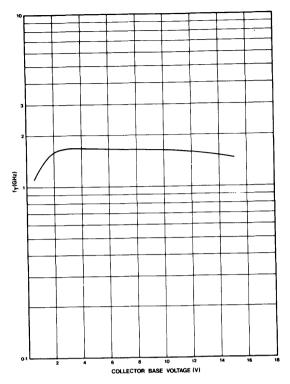

Fig. 2 Output capacitance ( $C_{OD}$ ) v. voltage

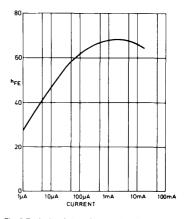

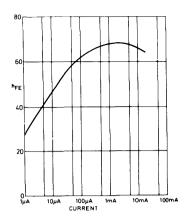

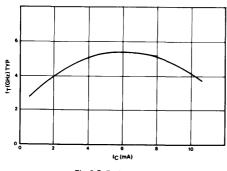

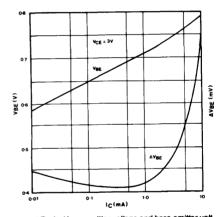

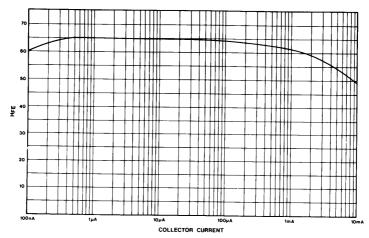

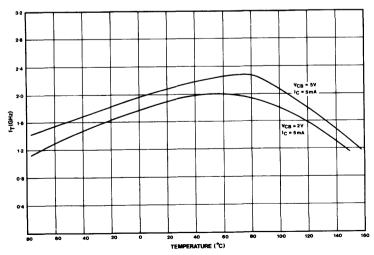

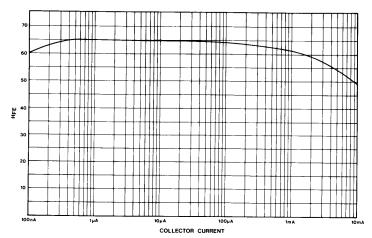

Fig. 3 Typical variation of hFE with collector current

### SL301K/SL301L

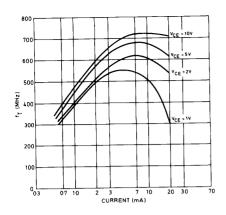

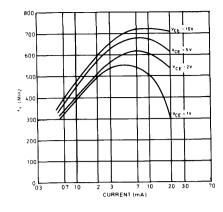

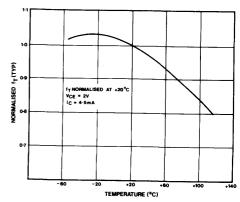

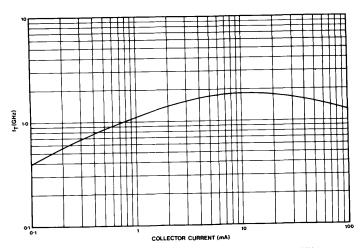

Fig. 4  $t_{TV}$ . collector curent ( $t_{T} = t h_{fe}$ . t = 100 MHz

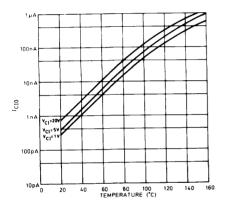

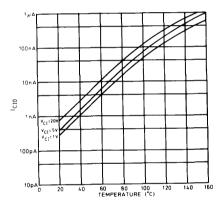

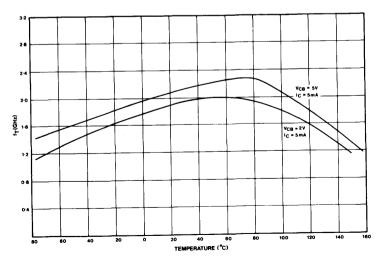

Fig. 6 Typical ICIO v. temperature

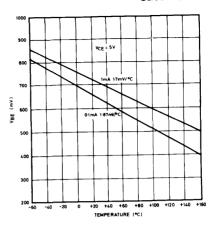

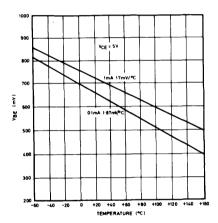

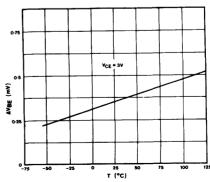

Fig. 5 VBE v. temperature

Fig. 7 Relationship between VCER and RBE

### SL301K/SL301L

### SL303L

### 400MHz TRIPLE NPN TRANSISTORS

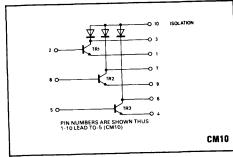

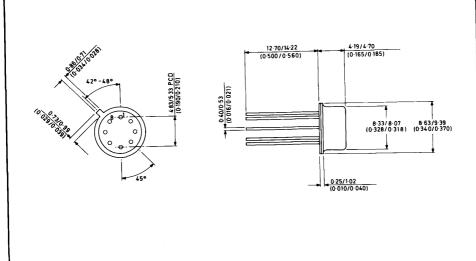

The SL303 is a silicon monolithic integrated circuit comprising three separate transistors, two of which have closely matched parameters; the third transistor may be used as, for example, a tail transistor. The SL303 devices are available in a 10-lead TO-5 (CM) package.

ORDERING CODES:

SL303L -- CM

### **FEATURES**

- Close VBE Matching

- High Gain

- Good Frequency Response

- **Excellent Thermal Tracking**

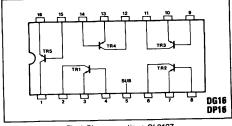

Fig. 1 Circuit diagram

### **APPLICATIONS**

- Differential Amplifier

- Comparator

### QUICK REFERENCE DATA

| Max voltage                 | 12V to 20V |

|-----------------------------|------------|

| Operating temperature range | +175°C     |

### **ABSOLUTE MAXIMUM RATINGS**

All electrical ratings apply to individual transistors: thermal ratings apply to total package dissipation.

The isolation pin must always be negative with respect to the collectors.

No one transistor may dissipate more than 75% of the

total power. -55°C to +175°C Storage temperature Chip operating temperature +175°C Chip-to-ambient thermal resistance: 425° C/W TO-5 (CM) Chip-to-case thermal resistance: see Note 1 265° C/W TO-5 (CM) 20V Vсво 12V VCEO 12V to 20V (see Figure 8) VCER

**4V VEBO** 25V Vcio 20mA 1<sub>CM</sub>

These figures are worst case, assuming all the power is dissipated in one transistor. If the power is equally shared between the three transistors, both thermal resistance figures can be reduced by 75° C/watt.

### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):

T<sub>amb</sub> = 25°C

| Characteristic                              | Complete      | Value |      |      | T     |                                 |  |  |

|---------------------------------------------|---------------|-------|------|------|-------|---------------------------------|--|--|

|                                             | Symbol        | Min.  | Тур. | Max. | Units | Conditions                      |  |  |

| Collector base breakdown                    | ВУсво         | 20    |      |      | V     | Ic = 10µA                       |  |  |

| Collector emitter breakdown                 | BVCEO         | 12    | 1    | ı    | Ιv    | Ic = 5mA                        |  |  |

| Emitter base leakage current                | lebo          | l     |      | 1    | μA    | VEB = 4V                        |  |  |

| Emitter base leakage current                | l EBO         |       |      | 10   | nΑ    | VEB = 2V                        |  |  |

| Collector isolation breakdown               | <b>BV</b> cio | 25    |      | 1    | l v   | Ic = 10uA                       |  |  |

| Forward current transfer ratio              | HFE           | 30    | 50   |      | 1     | $V_{CE} = 5V$ , $I_C = 10\mu A$ |  |  |

|                                             |               | 40    | 70   |      |       | Vce = 5V, Ic = 100µA            |  |  |

| 1                                           |               | 60    | 100  |      |       | VcE = 5V, Ic = 1mA              |  |  |

| _                                           |               | 50    | 80   |      |       | VCE = 5V, IC = 10mA             |  |  |

| Saturation voltage                          | VCE(SAT)      |       | 0.36 | 0.6  | l v   | Ic = 10mA, IB = 1mA             |  |  |

| _                                           | VBE(SAT)      | 0.7   | 0.8  | 0.9  | l v   | Ic = 10mA, IB = 1mA             |  |  |

| Base emitter saturation voltage             |               |       |      | 10   | nA    | V <sub>CB</sub> = 10V           |  |  |

| Collector base leakage current              | Ісво          | 1     |      | 10   | nA.   | V <sub>CB</sub> = 10V           |  |  |

| Collector isolation leakage current         | Icio          |       |      | 10   | nA    | Vci = 10V                       |  |  |

| Collector capacitance                       | Сов           | Í     |      | 2    | ρF    | VcB = 5V                        |  |  |

| Base capacitance                            | Сів           | - 1   | 1    | 4    | ρF    | V <sub>BE</sub> = 0V            |  |  |

| Collector isolation capacitance             | Ccio          | ı     |      | 6    | ρF    | Vci = +5V                       |  |  |

| Transition frequency                        | fτ            | 400   | 680  | _    | MHz   |                                 |  |  |

| Matching                                    |               | - 1   |      |      |       | ov, is simp                     |  |  |

| TR1 & TR2 only                              |               | - 1   |      |      |       |                                 |  |  |

| HFE1/HFE2                                   |               | 0.9   |      | 1.1  | l     | Vce = 5V, Ic = 100µA            |  |  |

|                                             |               | 0.9   |      | 1.1  | - 1   | Vce = 5V, Ic = 1mA              |  |  |

| Input offset voltage                        | ΔVBE          | ı     | i    | 3    |       | $V_{CE} = 5V, I_{C} = 100\mu A$ |  |  |

| _                                           | J             | 1     | l    | 3    |       | Vce = 5V, Ic = 1mA              |  |  |

| Temperature coefficient of ΔV <sub>BE</sub> |               |       |      | 10   |       | Vce = 5V, Ic = 100µA            |  |  |

| of input offset voltage                     | Tamb          |       |      |      |       | στ, το τουμπ                    |  |  |

Fig. 2 Output capacitance (Cob) v. voltage

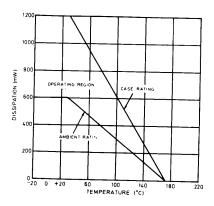

Fig. 3 Power dissipation derating curves (TO-5 package)

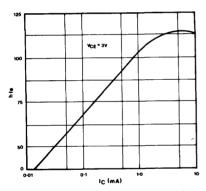

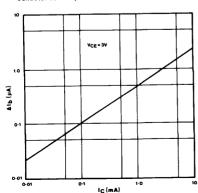

Fig. 4 Typical variation of hee with collector current

Fig. 5  $f_T$  v. collector current ( $f_T = f | h_{fe} | . f = 100$  MHz)

Fig. 6 V BE v. temperature

Fig. 7 Typical I<sub>CIO</sub> v. temperature

Fig.8 Relationship between VCER and RBE

### **SL360C & SL362C**

### HIGH PERFORMANCE NPN DUAL TRANSISTOR ARRAYS

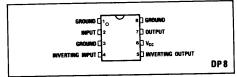

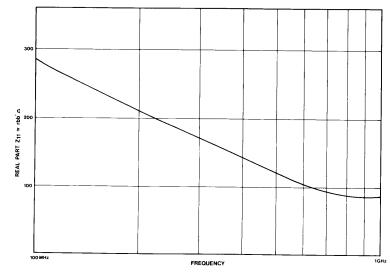

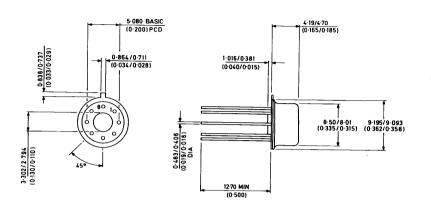

The SL360C and SL362C are high performance NPN dual transistor arrays fabricated as monolithic silicon devices. They feature accurate parameter matching and close thermal tracking. They have high transition frequencies (typ. 2.2GHz) and low device capacitance. In addition the SL362C offers good noise performance (1.6dB noise figure at 60MHz).

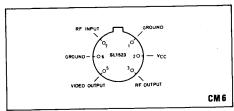

## SOLATION O O TO NC SOLITOR VIEW CM8

Fig. 1 Pin connections

### **APPLICATIONS**

- Instrumentation

- PCM Repeaters

- Analogue Signal Processing

- High Speed Switches Digital and Analogue

### **FEATURES**

- Accurate Parameter Matching.

- High f<sub>T</sub> (1.5GHz min., SL360)

- Low Noise (1.6dB at 60MHz SL362)

### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):

T<sub>amb</sub> = 22°C ± 2°C

| Characteristic                | Symbol      | Туре       | Value |      |      | Units | Conditions                                                      |  |  |

|-------------------------------|-------------|------------|-------|------|------|-------|-----------------------------------------------------------------|--|--|

| Characteristic                | Symbol      | туре       | Min.  | Тур. | Max. | Oille |                                                                 |  |  |

| Collector base breakdown      | ВУсво       | All        | 10    | 32   |      |       | lc = 10μA                                                       |  |  |

| Collector isolation breakdown | ВУсю        | All        | 16    | 60   |      | V     | $lc = 10\mu$                                                    |  |  |

| Emitter base leakage          | lево        | SL360/362C |       |      | 1    | μΑ    | V <sub>EB</sub> = 4V                                            |  |  |

| Emitter base leakage          | lebo        | SL360C     |       |      | 1    | nΑ    | VEB = 2V                                                        |  |  |

| Collector emitter breakdown   | LVCEO       | All        | 7     | 14   |      | V     | Ic = 5mA                                                        |  |  |

| DC current gain               | HFE         | SL360C     | 30    | 65   |      |       | V <sub>CE</sub> = 2V,I <sub>E</sub> = 5mA                       |  |  |

|                               |             | SL362C     | 30    | 70   |      | l     | V <sub>CE</sub> = 2V,I <sub>E</sub> = 1mA                       |  |  |

| Transition frequency          | fτ          | SL360C     | 1.5   | 2.2  | İ    |       | $V_{CE} = 2.5 \text{V I}_{E} = 5 \text{mA}, f = 200 \text{MHz}$ |  |  |

|                               |             | SL360E     | 1.6   | 3.2  |      |       | V <sub>CE</sub> = 5V,I <sub>E</sub> = 20mA                      |  |  |

|                               |             | SL360G     | 1.4   | 2.2  |      |       | $V_{CE} = 5.0V, I_F = 5mA, f = 200MHz$                          |  |  |

| Input offset voltage          | VBE1 - VBE2 | SL360C     |       | 3    | 10   | 1     | Vce = 2V,IF = 1mA                                               |  |  |

|                               | Į           | SL362C     |       | 5    |      | m∨    | V <sub>CE</sub> = 2V,I <sub>E</sub> = 1mA                       |  |  |

| Input offset current          | HFE1/HFE2   | All        | 0.9   | 1.0  | 1.1  | 1     | VCE = 2V,IE = 5mA                                               |  |  |

| Saturation voltage            | VCE(SAT)    | SL360C     |       | 0.25 | 0.6  | V     | IE = 10mA,IB = 1mA                                              |  |  |

| Noise figure                  | NF          | SL362C     | i     | 1.6  | 2.0  | dB    | 1                                                               |  |  |

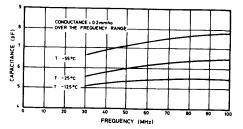

| Collector base capacitance    | Сов         | SL360C     |       | 0.5  | l    | pF    | V <sub>CB</sub> = 0V                                            |  |  |

|                               |             | SL362C     | i     | 1.3  | 1    |       | VcB = 0V                                                        |  |  |

| Collector isolation           | Ccı         | SL360C     |       | 2.3  |      | F .   | Vci = 0V                                                        |  |  |

| capacitance                   |             | SL362C     |       | 3.8  |      | pF    |                                                                 |  |  |

| Emitter base capacitance      | Сте         | SL360C     |       | 0.5  |      |       | 1                                                               |  |  |

| ·                             |             | SL362C     |       | 2.1  | 1    | 1 -   | 1                                                               |  |  |

| Forward base emitter voltage  | VBE(ON)     | SL360C     |       | 0.72 |      | V     | IE = 1mA,VCE = 2V                                               |  |  |

| Collector base leakage        | Ісво        | SL360C     |       | 1    | 1    | 1     | V <sub>CB</sub> = 10V                                           |  |  |

| Collector isolation leakage   | Icio        | SL360C     |       |      | 1    | nA    | Vci = 10V                                                       |  |  |

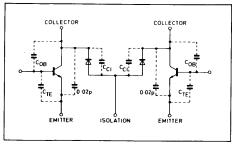

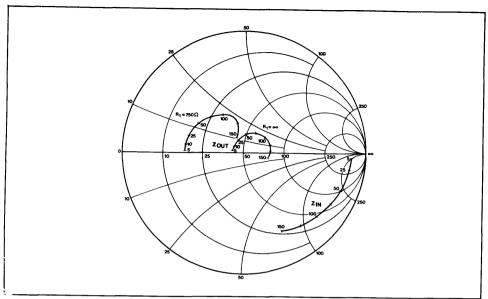

Fig.2 Equivalent circuit for SL360, SL362

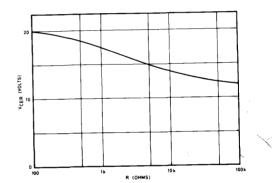

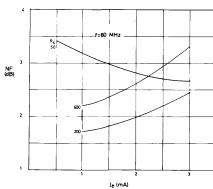

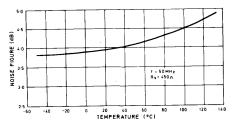

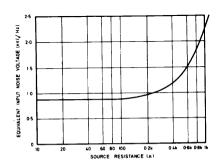

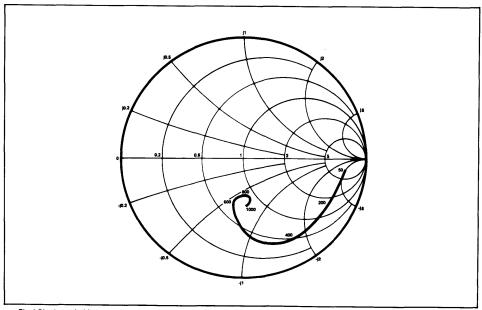

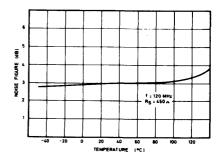

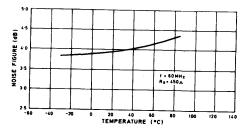

Fig. 4 Typical noise figure v source impedance for SL362

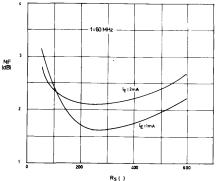

Fig. 3 Typical noise figure emitter current for SL362

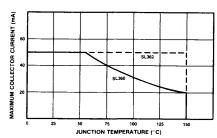

Fig.5 Max. continuous collector current vs junction temperature

### **ABSOLUTE MAXIMUM RATINGS**

All electrical ratings apply to individual transistors. Thermal ratings apply to the total package.

The absolute maximum ratings are limiting values above which life may be shortened or specified parameters may be degraded.

The isolation pin (substrate) must be connected to the

most negative point of the circuit to maintain electrical isolation between transistors.

### Electrical ratings

### Thermal ratings

|                                                    | CM8                      |

|----------------------------------------------------|--------------------------|

| Storage temperature Operating junction temperature | -55°C to +150°C<br>150°C |

| Thermal resistance (see Note 2)                    |                          |

| Chip-to-case<br>Chip-to-ambient                    | 265° C/W<br>425° C/W     |

### **NOTES**

1. The SL360G is also available to order. This meets RC5544 telecommunications requirements. SL360G has the SL360C characteristics with an additional fr guarantee as shown. 2. These figures are worst case, assuming all power is dissipated in one transistor. If the power is equally shared between the two transistors, both thermal resistance figures can be reduced by 50°C/watt.

### **SL440**

### **POWER CONTROL CIRCUIT**

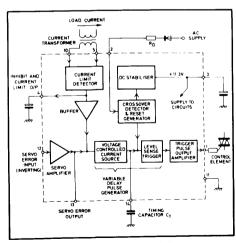

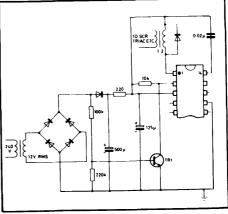

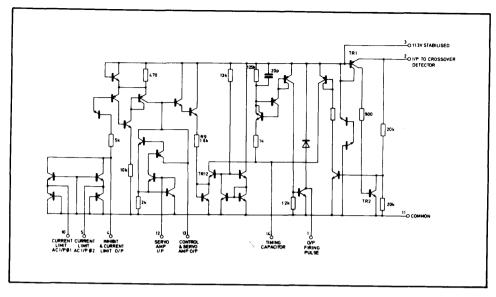

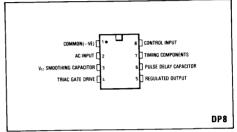

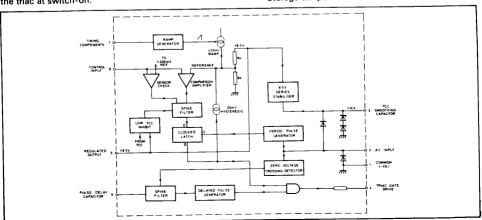

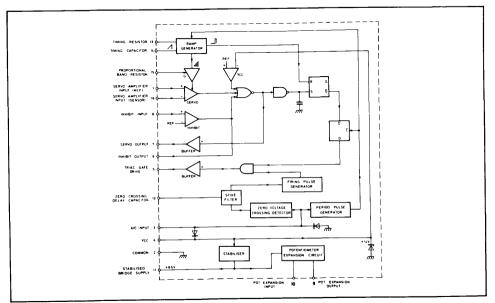

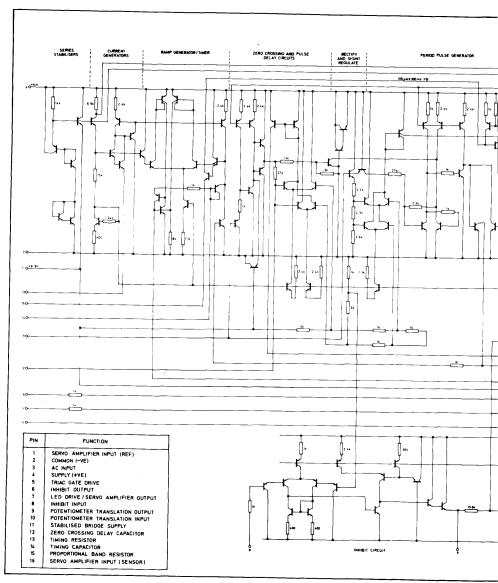

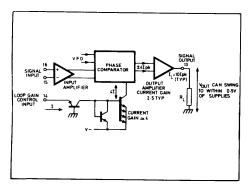

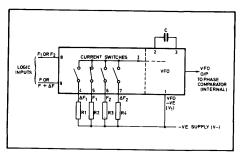

The SL440 is a versatile integrated circuit designed to provide variable-phase control of triacs and other power switching devices in a variety of domestic and industrial applications. The basic elements of the SL440 are shown in Fig.2.

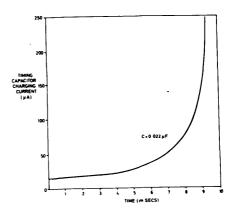

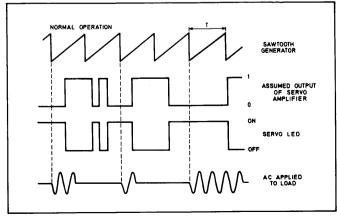

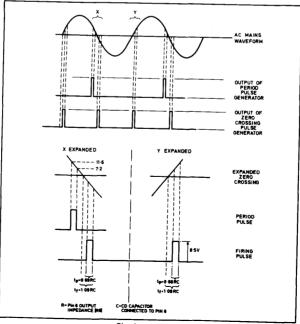

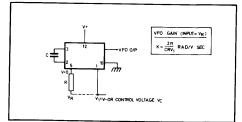

An external timing capacitor, C<sub>T</sub>, connected to pin 14 is discharged during positive and negative half cycles of the driving waveform (typically 50 Hz), at a constant rate which is proportional to the output of the servo amplifier (pin 13). When the charge reaches an internally-defined level, the conduction control circuit generates a 50µs (typ.) firing pulse (pin 1) to trigger the triac. The crossover detector resets the timing cycle when the driving waveform passes through zero, at which point C<sub>T</sub> is recharged rapidly. The servo amplifier thus controls the conduction time of the triac, and hence the power delivered to the load.

If the Inhibit input (pin 4) is taken below +5V (e.g. to pin 11) the conduction control circuit action is over-ridden and the firing pulses are inhibited. This facility can be used in conjunction with the current limit detector, by driving the AC input terminals (pins 5 and 10) from a current

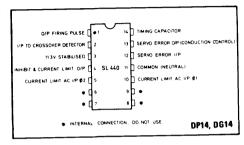

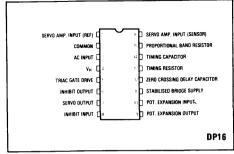

Fig. 1 Pin connections (top)

transformer in series with the load. If a load resistor is connected from pin 4 to the stabilised supply (pin 3), a DC voltage, inversely proportional to the AC load current, appears on pin 4. This is applied to the variable delay pulse generator as soon as the internally defined threshold voltage (approximately 5V) exceeds it, and so limits the load current.

### **FEATURES**

- Conduction Control

- Crossover Detector

- Servo Amplifier

- Internal Stabilised Supply (Available for External Circuitry)

- Total Power Shut-Down Facility

- AC Load Current Limitation

### **APPLICATIONS**

- Lamp Dimmers

- Automatic Lamp Faders

- Motor Speed Control

Fig.2 SL440 functional block diagram

### ELECTRICAL CHARACTERISTICS @ Tamb = +25°C

|           | Value    |                                   |                                       |                                                                                                                                                                                                 |  |  |

|-----------|----------|-----------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Min. Typ. |          | Max.                              | Units                                 | Conditions                                                                                                                                                                                      |  |  |

|           | 50       |                                   | μs                                    |                                                                                                                                                                                                 |  |  |

| 60        | 120      | I                                 | mA                                    |                                                                                                                                                                                                 |  |  |

| 15        | l        | 30                                | mA                                    | Rectified AC                                                                                                                                                                                    |  |  |

|           |          |                                   |                                       |                                                                                                                                                                                                 |  |  |

|           | 11.3     |                                   | +v                                    |                                                                                                                                                                                                 |  |  |

| i         |          |                                   |                                       |                                                                                                                                                                                                 |  |  |

| 0         | ļ.       | 5                                 | +v                                    |                                                                                                                                                                                                 |  |  |

|           |          |                                   |                                       | _                                                                                                                                                                                               |  |  |

|           | 75       |                                   | _                                     | Typical application, gain = $\frac{R_L}{2k}$                                                                                                                                                    |  |  |

|           | ±0.7     |                                   | v                                     | 2k                                                                                                                                                                                              |  |  |

|           | 60<br>15 | Min. Typ.  50 60 120 15 11.3 0 75 | Min. Typ. Max.  50 120 15 11.3 0 5 75 | Min.         Typ.         Max.         Units           60         120         μs mA mA           15         11.3         + V           0         5         + V           75         -         - |  |  |

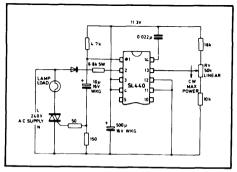

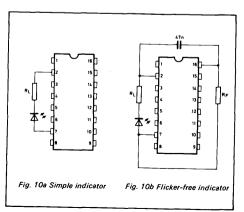

Fig.3 Lamp dimmer using minimum components

Fig.4 Autometic lamp fading circuit

### **APPLICATION NOTES**

A simple, manually-controlled, lamp dimmer circuit is shown in Fig.3. In this application, the servo amplifier is not used; proportional control of lamp brightness is effected by the voltage applied via RV1 to the servo amplifier output (pin 13) which is internally connected to the conduction control circuit.

A more sophisticated use of the SL440 is shown in Fig.4 an automatic lamp fading circuit which has applications in a variety of domestic environments. The circuit is used as follows: with S1 and S2 both open, the level of brightness is directly controlled by the setting of RV1. When S1 is closed, the positive voltage applied to pin 12 causes firing pulses to be produced at a conduction angle approaching 180° (fig.5) and the lamp brightness is maximum. When S2 is closed and S1 is opened, the servo amplifier acts as an integrator due to the Miller action of C1 and the lamp brightness fades progressively to the level previously set by RV1. The fade rate is determined by the choice of C1: for example, a 250 microfarad capacitor will result in a subjectively imperceptible fade rate of 20-30 minutes.

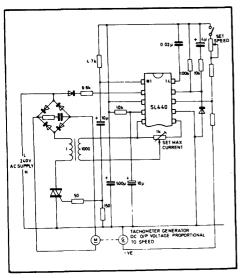

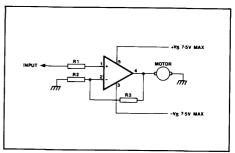

Fig.6 shows the SL440 used in a motor speed control circuit. The DC motor/tacho-generator is used in a velocity servo loop in which motor velocity is linearly proportional to the setting of RV1. RV2 controls the maximum motor current in the range 1 to 10A.

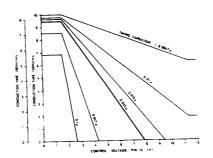

Fig.5 Triac conduction angle v. sinewave load power

### **OPERATING NOTES**

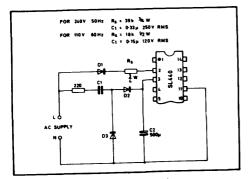

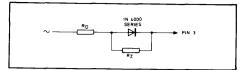

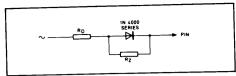

In applications where RF radiation is a problem, it is recommended that the filter circuit shown in Fig.7 be used.

Fig.6 Servomotor control with motor current limiting

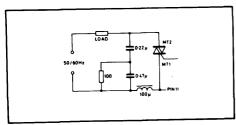

Where the SL440 is used for domestic light dimming, or in other applications where the power dissipated in the dropping resistor  $R_D$  is considered excessive, the series rectifier and dropping resistor can be replaced by the circuit shown in Fig.8. The series capacitor, together with the low impedance at pin 3, provides a degree of RF filtering at the AC supply terminals.

Fig. 7 RF filter for loads less than 100W or inductive. For loads of 100W and above, use 100μH and 0.1μF only.

Fig.8 Low loss power supply

Fig.9 Triac conduction time v. capacitor charging current

Fig.10 Triac conduction time v. servo amplifier output (demonstrating linear relationship)

Fig.11 Fully isolated supply operation of SL440, featuring full-wave crossover detection for symmetrical timing. Additional SL440s can be powered via separate 2001 feed resistors, synchronizing being achieved by connecting pin 2 of each SL440 to the collector of the common sync. transistor TRI.

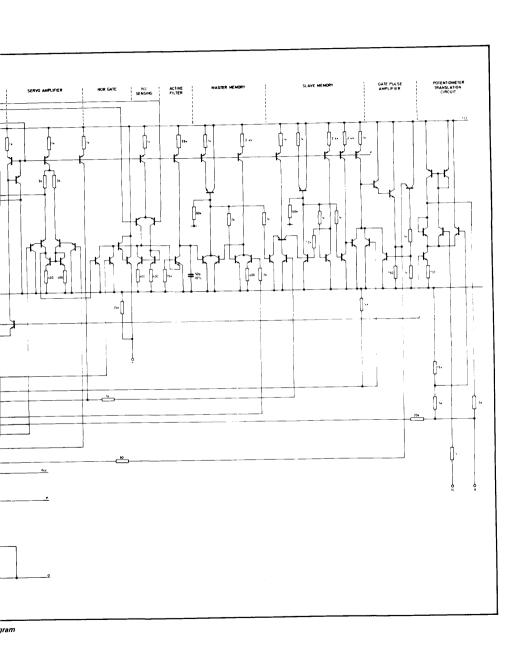

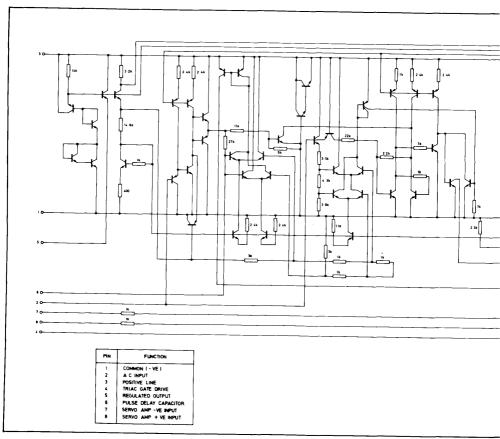

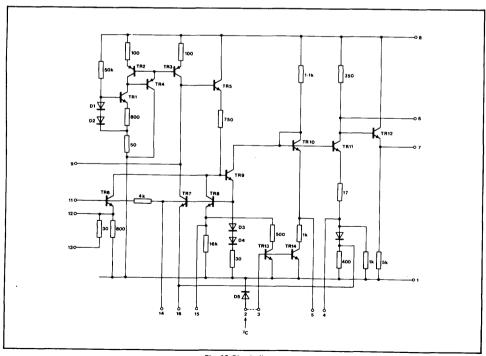

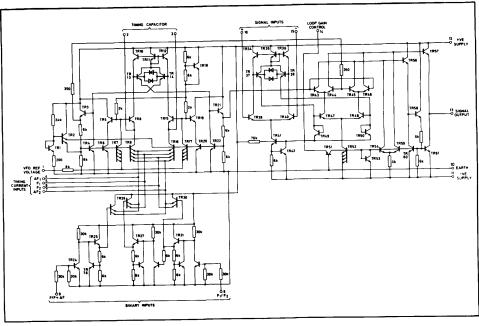

Fig. 12 Circuit diagram of SL440

### **ABSOLUTE MAXIMUM RATINGS**

Storage temperature Operating temperature Package dissipation Supply current to pin 2 -55°C to +125°C -10°C to +65°C 600 mW 200mA DC

### NOTE

Where the SL440 is to be used in a device socket, care should be taken to ensure that the reservoir capacitor on pin 3 is discharged before inserting the device. Failure to observe this precaution may result in damage to the internal shunt stabiliser.

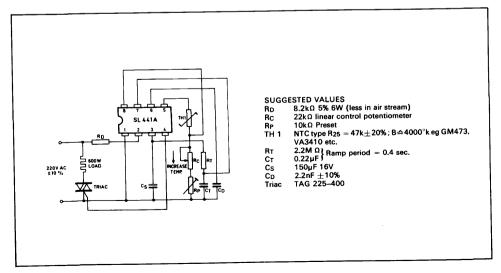

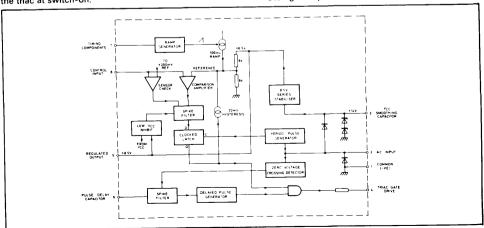

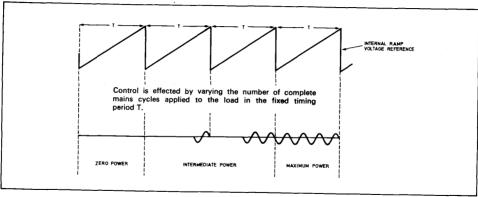

### SL441A ZERO VOLTAGE SWITCH

The SL441A is a symmetrical burst control integrated circuit in an 8 pin DIL package. When used with a triac, AC power may be regulated by varying the number of mains cycles applied to the load in a fixed timing period. The device is particularly suitable for temperature control applications including hairdyers, food warmers, soldering irons etc. Zero Voltage Switching has the advantage of minimising radio frequency interference.

### SPECIAL FEATURES

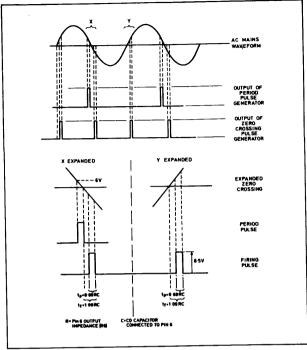

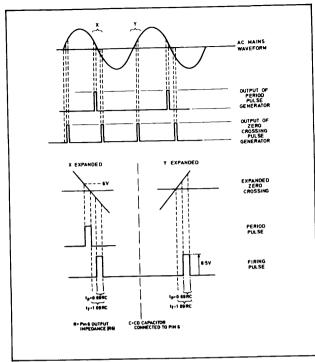

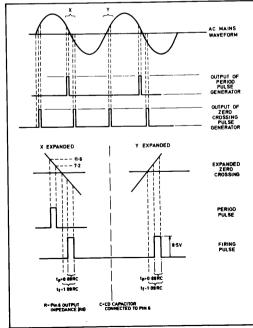

- 1. Balanced zero voltage point crossing detector, spike filter and pulse generator for reliable triggering of the triac.

- 2. A period pulse generator and bistable which are arranged to provide symmetrical burst control and eliminate ½ wave firing. (EN50.006, BS5406, 1976)

- 3. A ramp generator whose output is used to modify an internal reference voltage which is then compared with the voltage appearing on the thermistor to form a proportional control system. The period of the ramp generator is defined externally and may be chosen to limit 'lamp flicker' in accordance with EN50.006/ RS5406. 1976.

- 4. The comparison amplifier has inbuilt hysteresis to eliminate switching jitter and a spike filter/sampling circuit to provide high immunity to both spikes and coherent 50Hz/60Hz.

- 5. Thermistor malfunction may be sensed and power automatically removed.

- A supply voltage sensing circuit which inhibits firing pulses when the supply is inadequate to guarantee proper circuit operation. This eliminates stressing of the triac at switch-on.

Fig. 1 Pin connections

### **ABSOLUTE MAXIMUM RATINGS**

### Voltages

Voltage on pin 8 V<sub>8-1</sub> Max. 12V Voltage on pin 4 V<sub>4-1</sub> Max. 10V

### Currents

Supply current (pin 2) Peak value  $\pm 1_2$ M 50mA. Non-repetitive peak current (tp  $\leq 250\mu s$ )  $\pm 1_2$ SM 200mA.

Output current (pin 5) Max.5mA Short circuit protected.

Output current (pin 4) average value I<sub>4</sub>(AV)

Output current (pin 4) average value I4(AV) Max 5mA Short circuit protected.

### Temperature

Operating ambient temperature TAMB -10°C to +75°C

Storage temperature TsTG -30°C to +125°C

### **SL441A**

### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):

TAMB = 25°C

All voltages measured with respect to common (pin 1)

| Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Value                                                    |                                                                                    |                                                                                   |                                                                                      |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Min.                                                     | Тур.                                                                               | Max.                                                                              | Units                                                                                |  |

| Shunt regulating voltage pin 3 @ 16mA Shunt regulating voltage pin 3 @ 16mA @ 75°C Supply voltage trip level pin 3 Supply current (less I₄AV, I₅) (see Note 1) Regulated voltage pin 5 Regulated voltage temperature coefficient pin 5 Triac gate drive pin 4 (See Note 2) Open circuit ON voltage Open circuit OFF voltage Output current into 2V drain Output current into 4V drain Output current into short circuit Internal drain resistance Control input pin 8 Bias current Hysteresis Sensor malfunction circuit operates at Input working voltage range Internal reference voltage (Ramp start) Internal reference voltage (Ramp finish) Peak-to-peak amplitude of ramp Pin 6 output impedance (R6) (See Note 2) Maximum ripple voltage pin 3 | 8.0<br>-1<br>100<br>65<br>150<br>0<br>4.0<br>360<br>21.5 | 14.7<br>12.2<br>8.5<br>8.5<br>130<br>80<br>800<br>200<br>4.25<br>4.67<br>420<br>27 | 16<br>7.5<br>9.0<br>+1<br>0.1<br>200<br>1<br>250<br>12<br>4.5<br>480<br>32.5<br>1 | V<br>V<br>V<br>M<br>V/°C<br>V<br>MA<br>MA<br>MA<br>MA<br>MV<br>WV<br>V<br>WV<br>VP−P |  |

### NOTES

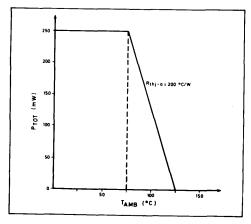

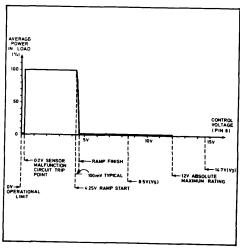

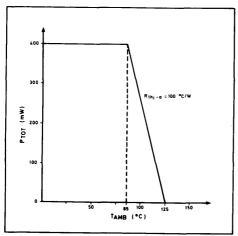

Fig. 3 Power dissipation

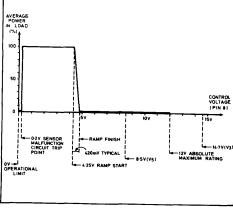

Fig. 4 Control characteristic

<sup>1.</sup> The supply current is 0.45 × (RMS current fed into pin 2). I<sub>5</sub> is the current drained from pin 5 externally. I<sub>4AV</sub> is the average triac gate current supplied each mains cycle. current supplied each mains cycle.

2. Triac firing pulse.  $t_p$  Pulse width  $t_p$  Pulse width  $t_p$  Pulse width  $t_p$  Pulse width  $t_p$  Nominal ( $C_D = 2.7 nF$ )  $t_p = 50 \mu s$   $t_p = 5$

Fig. 5 Pulse timing

### **APPLICATIONS**

Setting up

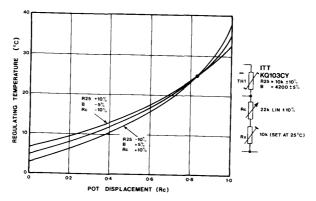

With R<sub>C</sub> at zero resistance, adjust R<sub>P</sub> to give the maximum output air temperature desired (eg 80°C). The value of R<sub>C</sub> will determine the minimum regulated output air temperature (eg 40°C).

Fig. 6 Application circuit for temperature regulated hairdryer

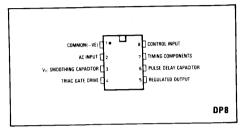

# SL441C ZERO VOLTAGE SWITCH

The SL441C is a symmetrical burst control integrated circuit in an 8 pin DIL package. When used with a triac, AC power may be regulated by varying the number of mains cycles applied to the load in a fixed timing period. The device is especially suited to room temperature control applications including panel heaters, fan heaters etc. Zero Voltage Switching has the advantage of minimising radio frequency interference.

#### SPECIAL FEATURES

- 1. Balanced zero voltage point crossing detector, spike filter and pulse generator for reliable triggering of the triac.

- 2. A period pulse generator and bistable which are arranged to provide symmetrical burst control and eliminate ½ wave firing. (EN50.006, BS5406, 1976)

- 3. A ramp generator whose output is used to modify an internal reference voltage which is then compared with the voltage appearing on the thermistor to form a proportional control system. The period of the ramp generator is defined externally and may be chosen to limit 'lamp flicker' in accordance with EN50.006/BS5406, 1976.

- The comparison amplifier has inbuilt hysteresis to eliminate switching jitter and a spike filter/sampling circuit to provide high immunity to both spikes and coherent 50Hz/60Hz.

- Thermistor malfunction may be sensed and power automatically removed.

- 6. A supply voltage sensing circuit which inhibits firing pulses when the supply is inadequate to guarantee proper circuit operation. This eliminates stressing of the triac at switch-on.

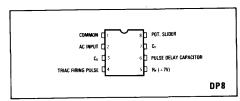

Fig. 1 Pin connections

#### **ABSOLUTE MAXIMUM RATINGS**

#### Voltages

Voltage on pin 8 V<sub>8-1</sub> Max. 12V Voltage on pin 4 V<sub>4-1</sub> Max. 10V

#### Currents

Supply current (pin 2) Peak value  $\pm 1_2M$  50mA. Non-repetitive peak current (tp  $\leqslant$  250 $\mu$ s)  $\pm 1_2SM$  200mA.

Output current (pin 5) Max. 5mA Short circuit protected.

Output current (pin 4) average value I<sub>4</sub>(AV)

Max 5mA Short circuit protected.

#### Temperature

Operating ambient temperature TAMB -10°C to +75°C

Storage temperature TsTG-30°C to +125°C

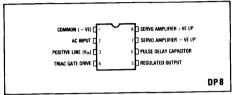

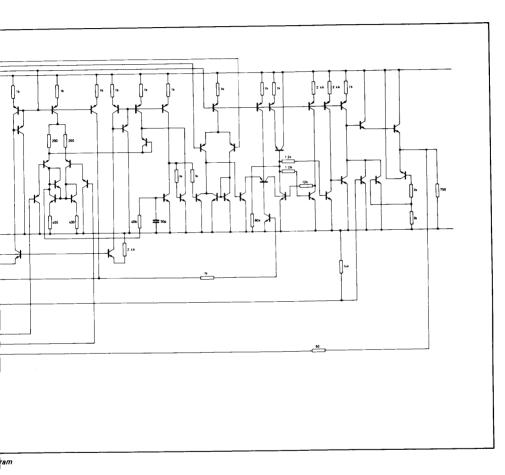

Fig. 2 Block schematic of SL441C

## **ELECTRICAL CHARACTERISTICS**

#### Test conditions (unless otherwise stated):

TAMB = 25°C

All voltages measured with respect to common (pin 1)

| Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                         |                                                                                    |                                                                                   |                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Min.                                                    | Тур.                                                                               | Max.                                                                              | Units                                                                                                                                                         |

| Shunt regulating voltage pin 3 @ 16mA Shunt regulating voltage pin 3 @ 16mA @ 75°C Supply voltage trip level pin 3 Supply current (less I4AV, I5) (see Note 1) Regulated voltage pin 5 Regulated voltage temperature coefficient pin 5 Triac gate drive pin 4 (See Note 2) Open circuit ON voltage Open circuit OFF voltage Output current into 2V drain Output current into 2V drain Output current into short circuit Internal drain resistance Control input pin 8 Bias current Hysteresis Sensor malfunction circuit operates at Input working voltage range Internal reference voltage (Ramp start) Internal reference voltage (Ramp finish) Peak-to-peak amplitude of ramp Pin 6 output impedance (R6) (See Note 2) Maximum ripple voltage pin 3 | 8.0<br>-1<br>100<br>65<br>150<br>0<br>4.0<br>70<br>21.5 | 14.7<br>12.2<br>8.5<br>8.5<br>130<br>80<br>800<br>200<br>4.25<br>4.35<br>100<br>27 | 16<br>7.5<br>9.0<br>+1<br>0.1<br>200<br>1<br>250<br>12<br>4.5<br>130<br>32.5<br>1 | V<br>V<br>V<br>MA<br>V<br>V<br>MA<br>MA<br>MA<br>MA<br>MV<br>MV<br>WV<br>V<br>V<br>V<br>V<br>V<br>MV<br>V<br>V<br>V<br>MV<br>V<br>V<br>V<br>MV<br>V<br>V<br>V |

#### NOTES

1. The supply current is 0.45 × (RMS current fed into pin 2). I<sub>5</sub> is the current drained from pin 5 externally. I<sub>4AV</sub> is the average triac gate current supplied each mains cycle.

2. Triac firing pulse. tp Pulse width 0.69 R6Cpµs typical

tr Pulse finish 1.09 R6C<sub>D</sub> μs minimum after zero voltage point R6 in kΩ, C<sub>D</sub> in nF See Application circuit

$t_p$  Nominal ( $C_D = 2.7 nF$ ) =  $50 \mu s$  $t_f$  Minimum ( $C_D = 2.7 nF$ ) =  $63 \mu s$

3. Ramp period  $0.85 \pm 0.15 \times R_T C_T$  sec. See Application circuit. The actual value of  $R_t$  must lie between  $500k\Omega$  and  $3M\Omega$ .

38

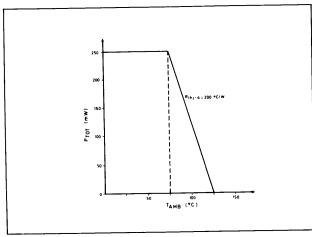

Fig. 3 Power dissipation

Fig. 4 Control characteristic of pin 8

Fig. 5 Pulse timing

#### **APPLICATIONS**

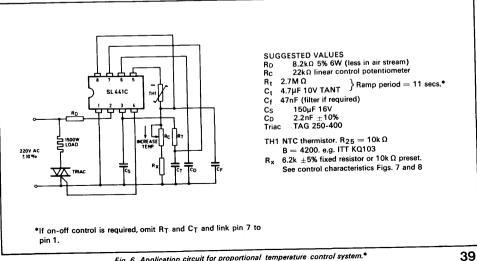

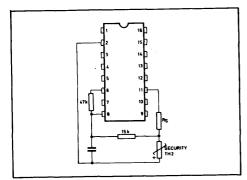

#### Electronic thermostat for room heater

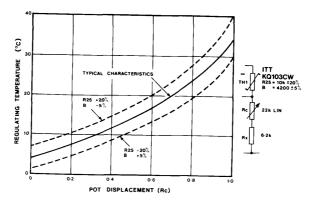

The circuit in Fig. 6 has a sensitivity of nominally 100mV/°C. The width of the proportional control band is nominally 1.0°C and offers a good compromise between temperature stability and regulation performance. For potentiometer control characteristics see Figs. 7 and 8.

Fig. 6 Application circuit for proportional temperature control system.\*

Fig. 7 Control characteristics of electronic room thermostat (mechanical calibration)

Fig. 8 Control characteristics of electronic room thermostat (electrical calibration)

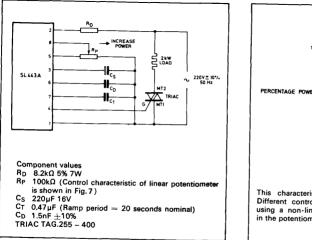

# SL443A zero voltage switch

The SL443A is a symmetrical burst control integrated circuit in an 8-pin DIL plastic package and is mainly intended for manual heat control applications, for example cooker hot plates and powerful hair dryers.

#### SPECIAL FEATURES

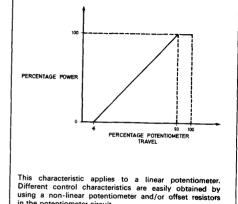

- Well defined load power/potentiometer displacement characteristics

- 2. High immunity against spurious triac firing under noisy mains environment (automatic spike filtration)

- 3. Enables compliance with Cenelec EN50,006/ BS5406-1976

- (A) Switching rate controlled

- (B) symmetrical burst control

- . Very low external component count

- 5. Triac firing pulses inhibited whilst the ICIs power supply is being established.

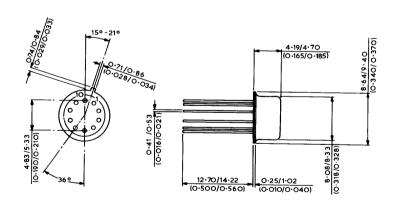

Fig. 1 Pin connections (top)

#### **APPLICATIONS**

- Cooker hotplates

- Powerful hairdryers

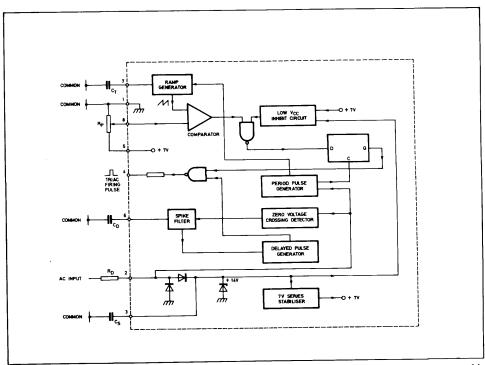

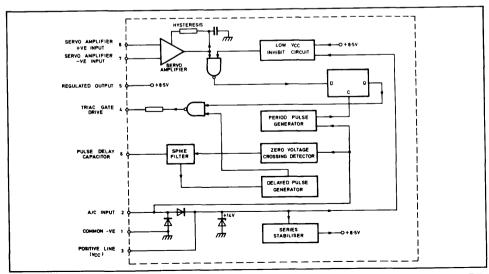

Fig. 2 SL443A block diagram

#### CIRCUIT DESCRIPTION

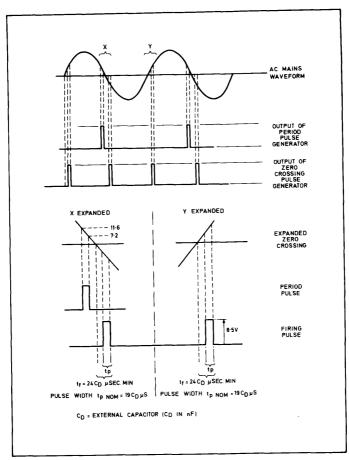

The externally current limited AC supply is applied to the device, and rectification followed by shunt regulation provides a 14V DC supply. This is externally smoothed before application to the 7.0V series stabiliser which feeds the resistance bridge. The stabiliser must be within regulation, or operation of the 'Low Vcc Inhibit' circuit will result. This circuit overrides all other circuitry and prevents unsuitable firing pulses from being supplied to the triac at 'switch-on'. The current limited AC supply also drives the Period Pulse Generator (PPG) and zero voltage crossing circuits.

The PPG produces a single short duration pulse for each completed mains cycle and serves two purposes. Firstly it is used to clock logic information such that the circuit behaves in a symmetrical manner and only complete mains cycles are applied to the load. Secondly the pulse is used to switch timing components in the ramp generator and this enables long time constants to be achieved without having to resort to the use of

electrolytic capacitors.

The zero voltage crossing detector controls a pulse generator that has a delayed output. The delay is necessary since, with loads that are slightly inductive or low power resistive, the triac load current may not reach its required holding level at zero voltage point.

Both delay and pulse duration are defined by an external capacitor and this further serves the purpose of filtering out spikes which occur in the zero crossing region. Automatic rejection takes place of spikes having a duration of up to 50 per cent of the normal width of the triac firing pulse.

The comparator amplifier has differential linputs and these are used to compare the potential appearing on the slider of the control potentiometer with that of the ramp waveform. The output of this amplifier controls the logic circuitry and the potentiometer setting defines the fraction of the ramp period for which the triac is in conduction so controlling the power in the load.

#### **ELECTRICAL CHARACTERISTICS**

#### Test Conditions (unless otherwise stated)

TAMB == 25°C.

All voltages measured with respect to common (pin 1)

|                                                                                    |               | Value                      |               |               |                                                             |

|------------------------------------------------------------------------------------|---------------|----------------------------|---------------|---------------|-------------------------------------------------------------|

| Characteristic                                                                     | Min.          | Тур.                       | Max.          | Units         | Conditions                                                  |

| Shunt regulating voltage pin 3<br>Shunt regulating voltage pin 3                   |               | 14.7                       | 16            | V             | l3 = 16mA<br>l3 = 16mA,                                     |

| Supply voltage trip level pin 3 •Supply current (less I4 AV, 2×I5) See Note 1      |               | 12.2                       | 7.2           | V<br>mA       | T <sub>amb</sub> = +75°C                                    |

| Potentiometer supply pin 5, V <sub>5</sub> Potentiometer resistance range          | 6.8<br>18     | 7.0                        | 7.6<br>140    | V             |                                                             |

| Triac gate drive pin 4 Open circuit ON voltage                                     |               | 8.5                        | İ             | V             |                                                             |

| Open circuit OFF voltage Output current into 2V drain Output current into 4V drain | 80<br>50      | 100                        | 0.1           | W<br>mA       |                                                             |

| Output current into short circuit Internal drain resistance                        | 50            | 70<br>800                  | 200           | mA<br>mA<br>Ω |                                                             |

| Control input pin 8 Bias current                                                   |               | 800                        | 1             | μ <b>Α</b>    |                                                             |

| Internal reference – ramp start<br>– ramp finish                                   | 0.3<br>V5 0.5 | 0.5<br>V <sub>5</sub> –0.3 | 0.7<br>V5 0.1 | , ,           |                                                             |

| * Period of ramp generator – T                                                     | 27            | 30                         | 33            | s             | $(R_P = 100K, C_t = 0.68\mu)$<br>(RMS mains voltage = 220v) |

| Pin 6 output impedance R6                                                          | 21.5          | 27                         | 32.5          | kΩ            | <b>0</b>                                                    |

- The supply current is 0.45 x (RMS current fed into Pin 2)

- $\bigstar$  Period of ramp = T = 2 × C<sub>T</sub> × R<sub>P</sub> × (RMS mains voltage) seconds

## ABSOLUTE MAXIMUM RATINGS

Voltages

Voltage on pin 8, Voltage on pin 4,

V8-1 V4-1 Max 10v 10v Max

Currents

Supply current, pin 2 peak value ± I2M Non-repetitive peak current (tp ≥ 250µS) ± l2sм Output current, pin 5 Is Output current, pin 4, average value I4 (AV)

50mA Max 200mA Max Short circuit protected 10mA Max Short circuit protected

Temperatures

Operating ambient temperature Storage temperature **Power Dissipation**

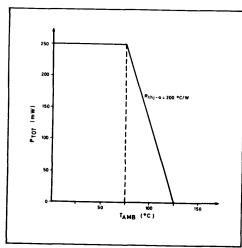

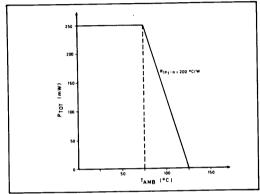

Тамв -10 to 75°C Tstg -55 to +125°C See Fig. 3

Fig. 3 Power dissipation

Fig. 4 Method of control

Fig. 5 Method of control

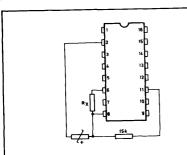

Fig. 6 Cooker hotplate control

in the potentiometer circuit.

Fig. 7 Output power v. potentiometer displacement

# SL445A ZERO VOLTAGE SWITCH

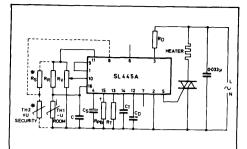

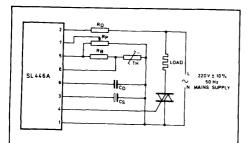

The SL445 is a triac controller providing a complete solution for temperature controlled electric panel heaters, cookers, film processing baths etc.

Switching occurs at the zero voltage point in order to minimise radio frequency interference.

The device is suitable for mains on-line operation and requires minimal external components.

#### SPECIAL FEATURES

- 1. Choice of proportional or on/off temperature control.

- Controlled switching rate in order to limit 'lamp flicker' (as per EN50,006). A pulse integration technique eliminates the problems associated with electrolytic timing capacitors.

- 3. Very accurate temperature control is possible since switching jitter has been eliminated without introducing hysteresis to the servo amplifier.

- 4. Symmetrical burst control i.e. no half-wave firing (as per EN50,006).

- 5. LED drive circuit which responds directly to the temperature setting.

- Over-temperature protection circuit using a fail-safe PTC thermistor and having the option of automatic or manual reset.

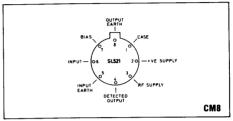

Fig. 1 Pin connections (top)

- LED/Buzzer drive circuit controlled by 6 above.

- 8. High immunity against spurious triac trigger pulses under noisy mains environment.

- Spurious triac trigger pulses inhibited at 'switch-on'.

Potentiometer expansion circuit to improve resolution/reduce component count.

#### SL445A

#### **CIRCUIT DESCRIPTION**

The externally current limited AC supply is applied to the device and rectification followed by shunt regulation produces a 14V DC supply.

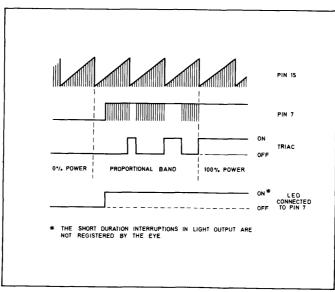

This is externally smoothed before application to the 8.5V series stabiliser which must be within regulation or operation of the 'Low Vcc Inhibit' circuit will result. This latter circuit overrides all other circuitry and prevents unsuitable firing pulses from being supplied to the triac at 'switch-on'. The current limited AC supply also drives the Period Pulse Generator (PPG) and Zero Voltage Crossing circuits.

The PPG produces a single short duration pulse for each completed mains cycle and serves two purposes. Firstly it is used to clock logic information such that the circuit behaves in a symmetrical manner and only complete mains cycles are applied to the load. Secondly the pulse is used to switch timing components in the ramp generator and this enables long time constants to be achieved without having to resort to the use of electrolytic capacitors.

The Zero Voltage Crossing Detector controls a pulse generator that has a delayed output. This delay is necessary since with loads that are slightly inductive or low power resistive, the triac load current may not reach its required holding level at the zero voltage point.

Both delay and pulse duration are defined by an external capacitor and this further serves the purpose of filtering out spikes which occur in the zero crossing region. Automatic rejection takes place of spikes having a duration of up to 50 per cent of the normal width of the triac firing pulse.

The Servo Amplifier has differential inputs and these are used to sense the output of the bridge containing the room temperature sensing thermistor. The output of this amplifier is NOR-gated with the outputs of the Inhibit Amplifier and the Low Vcc Amplifier.

The output of this gate is accessible such that it may

Fig. 3 Power dissipation

be used to control an LED so indicating whether or not the appliance is consuming electricity. The output from the NOR gate is also applied to an active spike filter before application to the S input of the R/S Bistable. Since this bistable can only be reset once every ramp generator cycle, it follows that a definite limitation is imposed on the switching rate of the system and this enables compliance with the requirements of the EN50-006 regarding 'lamp-flicker'.

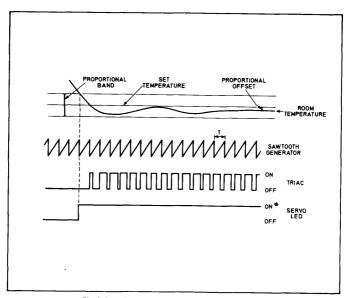

An externally defined proportion of the ramp waveform may be applied to the 'offset' of the Servo Amplifier such that the amplifier has an offset which varies linearly with time. This has the effect — as the bridge approaches balance — of varying the power output in proportion to the difference between the set temperature and the actual temperature i.e. Proportional Control. The advantage of this arrangement is that the approach of bridge balance is anticipated and overshoot is avoided.

The potentiometer expansion circuit matches the characteristics of a typical NTC thermistor to provide good resolution and linear temperature control over the normal domestic temperature range.

The Bridge is supplied with a stable 8.5V supply from the series stabiliser and one ninth of this supply is used as a reference voltage for the Inhibit Amplifier. This reference is compared with the voltage appearing across the PTC thermistor which is used to sense an overtemperature condition. The output of the Inhibit Amplifier is used to control the NOR gate which has already been mentioned and is also made accessible such that visual or audible warning may be provided. In addition, a suitable resistor may be connected between amplifier input and output to provide hysteresis should this be required. Choice of resistor value will determine whether the circuit works in an automatic or manual reset mode.

#### ABSOLUTE MAXIMUM RATINGS

| Pin                                                                 | Max. | Units |

|---------------------------------------------------------------------|------|-------|

| Applied voltage                                                     | V4   | V     |

| 3. Peak Repetitive Current in (±l2м) 3. Non-repetitive peak current | 80   | mA    |

| $(tp < 250 \mu S) \pm I_{2SM}$                                      | 200  | mA    |

| 5. Applied voltage                                                  | 10   | V     |

| 6. Applied Voltage                                                  | 10   | V     |

| 6. Output Current                                                   | 10   | mΑ    |

| 7. Applied Voltage                                                  | 6    | V     |

| 7. Output Current                                                   | 10   | mA    |

| 8. Applied Voltage                                                  | 10   | Ÿ.    |

| Applied Voltage                                                     | V11  | v     |

| 10. Applied Voltage                                                 | V11  | v     |

| 11. Output Current                                                  | 10 1 | mΑ    |

| 16. Applied Voltage                                                 | V4   | v     |

#### **ELECTRICAL CHARACTERISTICS**